Priscilla Wong

2013-11-12 19:15:07 UTC

Can someone help me on an issue I am seeing on my i2c-imx driver for

uClinux 2.6.29?

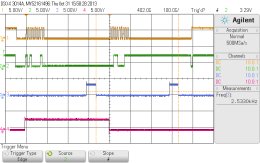

Attached is a scope capture of an i2c read operation. In the capture,

yellow is clock, green is data, blue and pink are both gpios I am using

for debugging. It can be seen that there is a 300 us delay after master

writes to the slave address. The transfer is complete when the interrupt

arrives and waitqueue is woken up. The pink gpio fires high during the

transfer complete call (i2c_imx_trx_complete) after the slave address is

written. The blue gpio fires high during the queue wake up call in the

ISR (i2c_imx_isr). When looking at this capture, my first inclination is

to bump the interrupt level and priority, hoping it will speed up the

ISR but it had no effect on the delay.

Any ideas what is causing this delay?

Thanks,

Priscilla

-------------- next part --------------

A non-text attachment was scrubbed...

Name: scope_14.png

Type: image/png

Size: 33761 bytes

Desc: not available

URL: <Loading Image... >

>

uClinux 2.6.29?

Attached is a scope capture of an i2c read operation. In the capture,

yellow is clock, green is data, blue and pink are both gpios I am using

for debugging. It can be seen that there is a 300 us delay after master

writes to the slave address. The transfer is complete when the interrupt

arrives and waitqueue is woken up. The pink gpio fires high during the

transfer complete call (i2c_imx_trx_complete) after the slave address is

written. The blue gpio fires high during the queue wake up call in the

ISR (i2c_imx_isr). When looking at this capture, my first inclination is

to bump the interrupt level and priority, hoping it will speed up the

ISR but it had no effect on the delay.

Any ideas what is causing this delay?

Thanks,

Priscilla

-------------- next part --------------

A non-text attachment was scrubbed...

Name: scope_14.png

Type: image/png

Size: 33761 bytes

Desc: not available

URL: <Loading Image...